SiPearl in EPI 3B4HPC, July 1<sup>st</sup>, 2022

> Jean-Marc Denis Chief Strategy Officer jean-marc.denis@sipearl.com

# -SiPearl corporate overview

### The European Server Processor Solution

**HQ: Maisons-Laffitte (Paris), France**

**Incorporated in June 2019**

**CEO and Founder, Philippe Notton**

#### **Design centers:**

- France: Maisons-Laffitte, Massy, Sophia Antipolis, Grenoble

- Germany: Duisburg (Düsseldorf)

- Spain: Barcelona

Key Personnel from Intel, Atos, ST, Marvell, Nokia, Mstar-Mediatek

HPC Targeted Architecture based on Arm Neoverse V1 cores

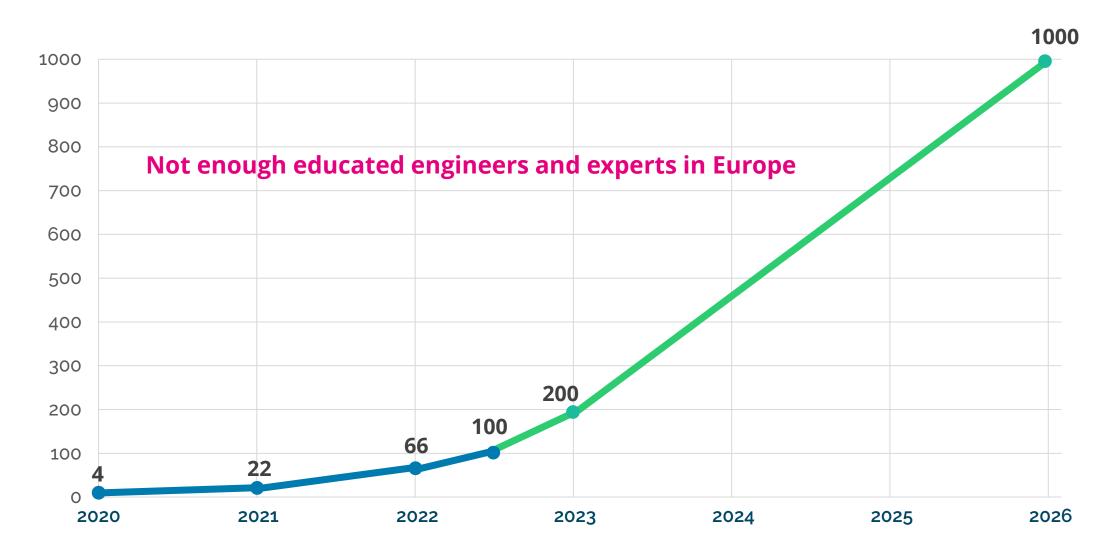

109 employees today, targeting >1,000 in 2025

### -SiPearl offices

#### We are close to our partners and customers

Official requests for new offices from local Trade Agencies: Italy, Switzerland, Canada

## -Headcount evolution 2020-2025

### Partnerships and ecosystem

# **GRAPHCORE**

More Coming Soon!

# EPI project factsheet

Phase 1 successfully concluded (2019-2021)

**Currently in Phase 2 (2022-2024)**

Consortium of 30 European academic and industrial partners from 11 countries

Funded by EuroHPC JU (50%) and co-funded by Croatia, France, Germany, Greece, Italy, the Netherlands, Portugal, Spain, Sweden and Switzerland

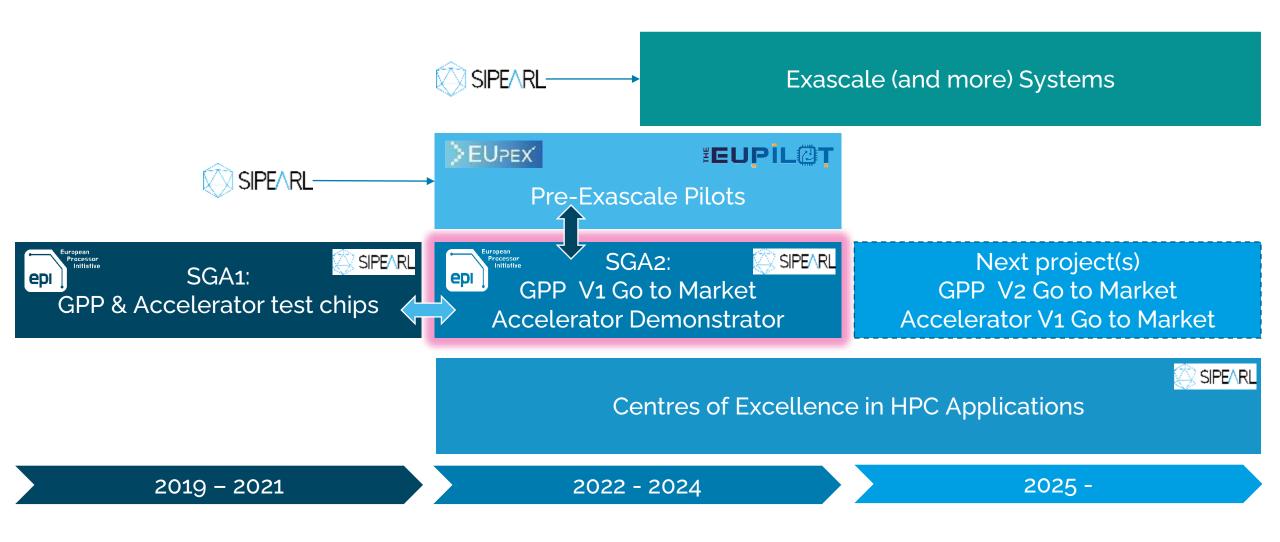

## —The ecosystem road to EU Exascale

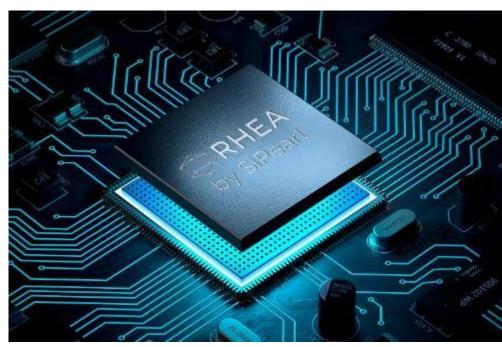

#### Rhea General Purpose Processor family Arm architecture Neoverse V1 cores Core SVE 256 per core supporting 64/32/BF16 and Int8 **ArmVirtualization extensions** Arm mesh fabric links Advanced RAS support including Arm RAS extensions arm arm arm SoC Link protection for NoC & high-speed IO ECC support for selected memory arm arm arm Large L3 (Shared Level Cache) Cache arm arm arm RAS supported for all cache levels HBM2e arm arm arm **Memory** And DDR5 ECC for memory and link protection for controllers 3rd party 3rd party inks Crypto 🕝 core core PCIe, CCIX & CXL High Speed I/O Root and endpoint support 3rd party 3rd party 3rd party core core core Other I/O USB, GPIO, SPI, I<sup>2</sup>C Power management block to optimize perf/watt **Power** across use cases and workloads. Management Secure boot and secure upgrade **Security Block** Crypto Support True random number generation Made in Europe

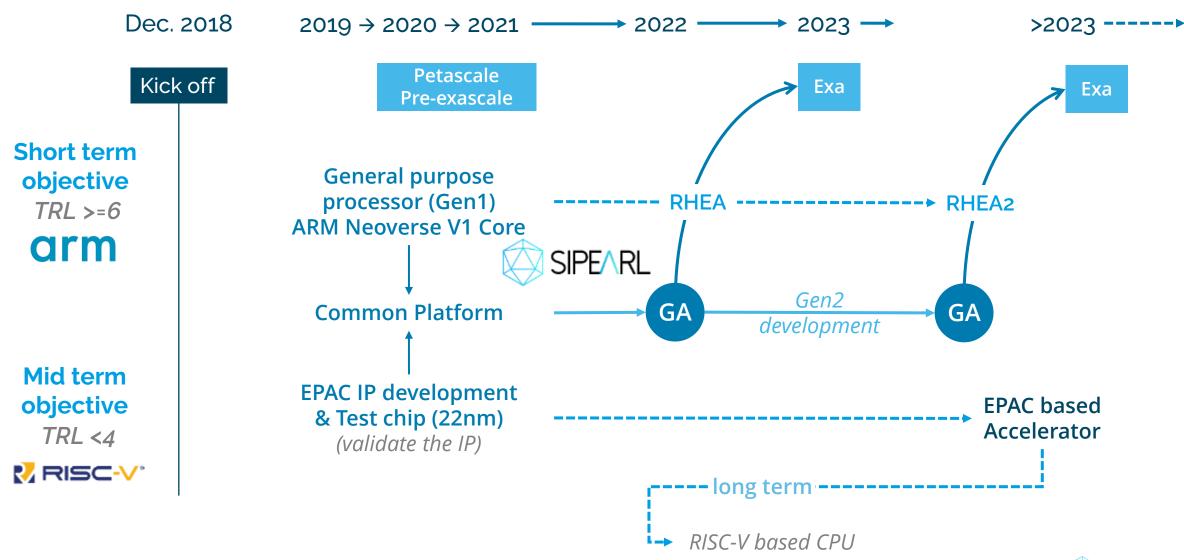

# -Overall roadmap: combine build and buy

# -EPI Common Platform enables EU Ecosystem

SiPearl chartered is also to develop the European Ecosystem SiPearl shares IP and benefits from IP ecosystem

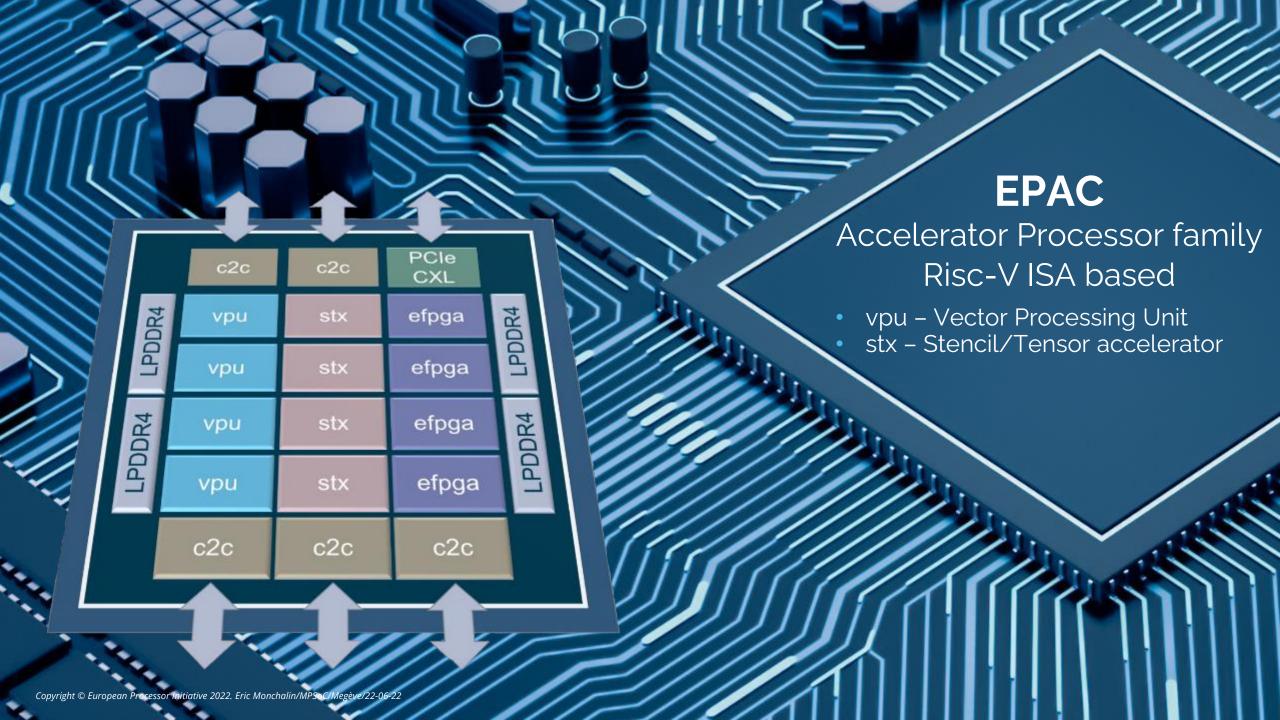

#### **Accelerator development (RISC-V based)**

- Al (tensor)

- Vector processing

- Stencil processing

- FPGA

---

#### **Packaging**

#### **IP** development

Staged integration: start with socket-to-socket connections and move into package (multi-chiplets) over time

Future: build IP (10y?)

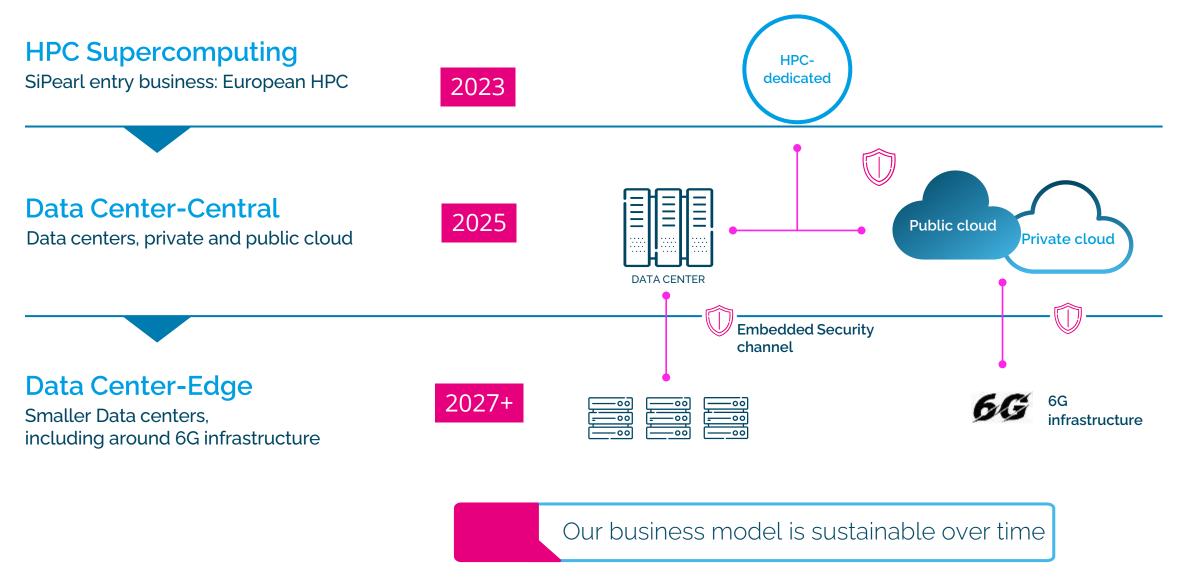

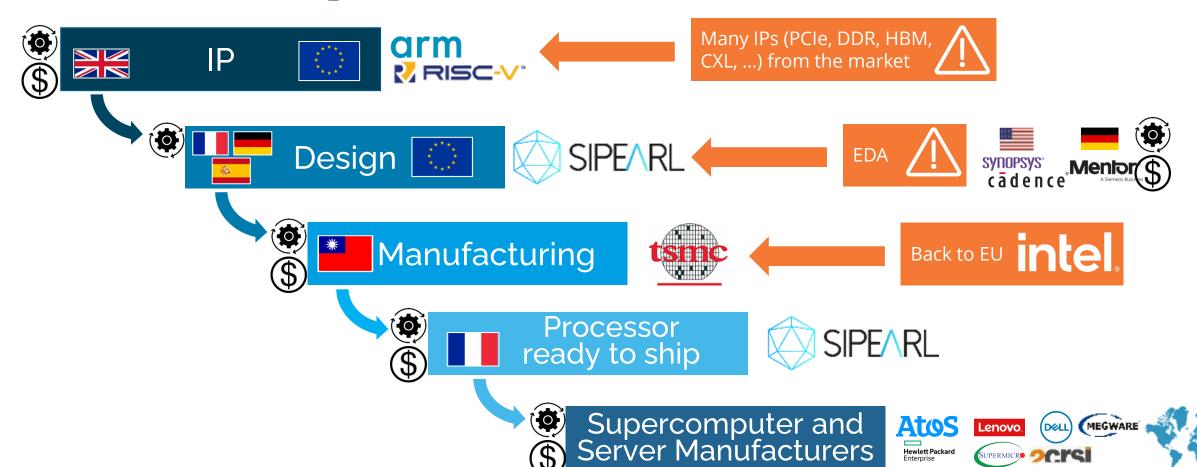

# -Sovereignty is coming on the top of classical business sustainability

# -Rhea: Designed in Europe

| Total: x V1 + 2 M7 Arm, 29 Risc-V, 4x SPUs. |                                  | Remarks          |                                      |

|---------------------------------------------|----------------------------------|------------------|--------------------------------------|

| Arm Neoverse V1 cores                       | Arm Neoverse V1                  | arm              | Including spare V1s.                 |

| Arm cortex-M7 cores                         | 2x Arm cortex-M7 = 2.            | arm              | for SCP and MCP subsystems.          |

| Risc-V in PMS                               | 1x Ariane + 1x ZeroRiscy = 2.    | <b></b> RISC-∨°  |                                      |

| Risc-V in SEG                               | 1x Ariane = 1.                   | <b>₹</b> RISC-V° | SEG for security element.            |

| Risc-V in STXs of 2x ERACs                  | 2x (1x Ariane + 8x Snitch) = 18. | <b>₹</b> RISC-V° | Snitch is a EU IP (stencil + tensor) |

| Risc-V in VRPs of 2x ERACs                  | 2x (4x VRP core) = 8.            | <b>₹</b> RISC-V° | VRP core is a modified Risc-V core.  |

| SPUs in STXs of 2x ERACs                    | 2x (2x SPU cores) = 4.           | <b>₹</b> RISC-V° | SPU core is a EU IP.                 |

- Some additional EU designed IP (power management, clock, cryptography) not counted here

- Not including  $\mu C$  cores used in Synopsys DDR controllers for the PHY training.

- ERAC: tests features, perf/mm2 and perf/w in 6nm. Competitiveness?

| Core   | Performance for the core.                 |

|--------|-------------------------------------------|

| V1     | 2x 256 SVE = 16 DP FLOPs/cycle; 2.5GHz@N6 |

| Snitch | 1x 64b FPU = 2 DP FLOPs/cycle; >1GHz@N6   |

| SPU    | 4x 32b FPU = 8 SP FLOPs/cycle; >1GHz@N6   |

### Arm Software Ecosystem: the most exhaustive, Open and proprietary Is Sovereignty a concern?

Networking & System

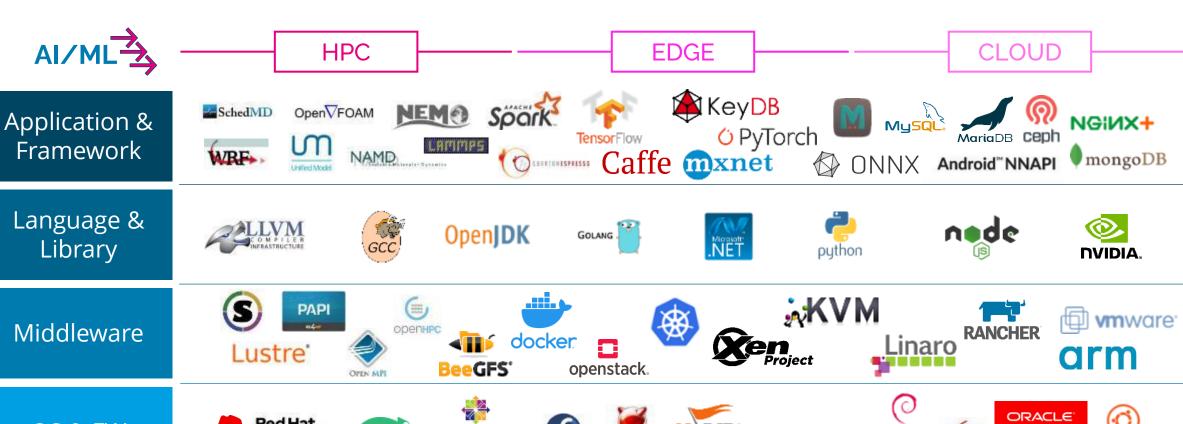

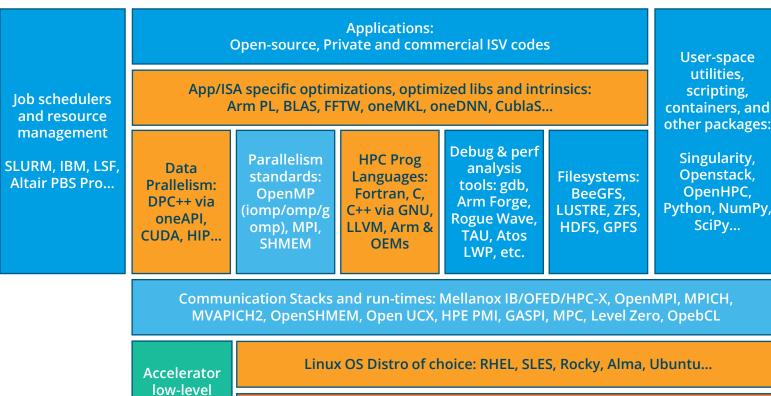

### Software stack: EU is already 100% sovereign. HPC centers & EuroHPC play a central role.

We rely on standards to ensure portability and compatibility for the customers; and to avoid vendor lock-in. Our goal is to make our design easy to use efficiently, including in the software stack by avoiding proprietary elements wherever feasible.

#### ISA:

Short-Mid term: ARM Long term: RISC-V or ARM

Gated by ecosystem, liability, fragmentation, ...

#### Preferred SW partners:

#### **OpenSource communities ARM System OEMs Accelerator partners**

- Graphcore

- Intel (oneAPI/SYCL...)

- Nvidia

#### **ISV** and **System** stack providers **Cloud solution ecosystem**

- Azure

- AWS

utilities, scripting, containers, and other packages: Cluster Singularity, Management Openstack,

OpenHPC,

SciPy...

**HPE Cluster** Management, **Atos SMC & SMC** xScale, xCat, Warewulf...

Tools:

SiPearl SW/FW development

software

SiPearl dev work on partner/open SW

Partner/open sW with SiPearl additions/updates

Arm Server Ready Plateform: Standard OS compatible FW and RAS features

**Accelerator Partner SW**

# Build and Buy

### Build ( ) vs buy ( ) : Value chain

**Atos**

Hewlett Packard

MEGWARE

CONSULTING SIGNIFICANT TYPICAL ALTHOUGH NETWORKS RISK MANAGING PUBLIC THEREBY

TYPICALLY

RATES YEARS **EXPERIENCE**

#### About SiPearl

Created by Philippe Notton, SiPearl is designing the high-performance, low-power microprocessor for European exascale supercomputers. This new generation of microprocessors will enable Europe to set out its technological sovereignty in strategic high performance computing markets such as artificial intelligence, medical research or climate modelling.

SiPearl is working in close collaboration with its 27 partners from the European Processor Initiative (EPI) consortium - leading names from the scientific community, supercomputing centres and industry - which are its stakeholders, future clients and end-users.

SiPearl employs 110\* people in France (Maisons-Laffitte, Grenoble, Massy, Sophia Antipolis), Germany (Duisburg) and Spain (Barcelona).

The company is supported by the European Union (funding from the European Union's Horizon 2020 research and innovation program under specific grant agreement no.826647).

\* as of June 30th 2022

Contact

Jean-Marc Denis

Chief Strategy Officer

jean-marc.denis@sipearl.com