Computer Architecture and Codesign

-

COTS multicore real-time systems

We develop new methods to derive reliable Worst-Case Execution Time (WCET) bounds for programs running in Commercial-off-the-shelf (COTS) multicore processors with unknown interference in the access to hardware shared resources.

-

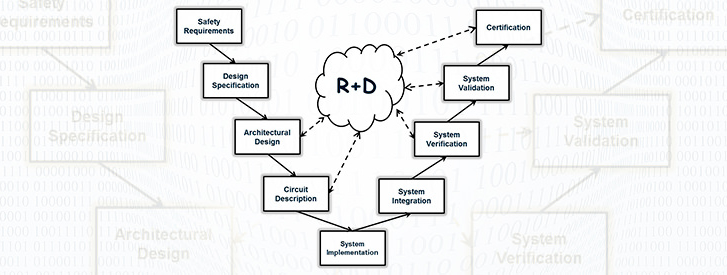

Dependable and power-efficient real-time systems

We propose several methodologies, techniques, and tools to help with the development of reliable and power-efficient real-time systems. Our designs are done in compliance with the safety-critical standards applicable in the corresponding domain (e.g. ISO26262 for automotive).

-

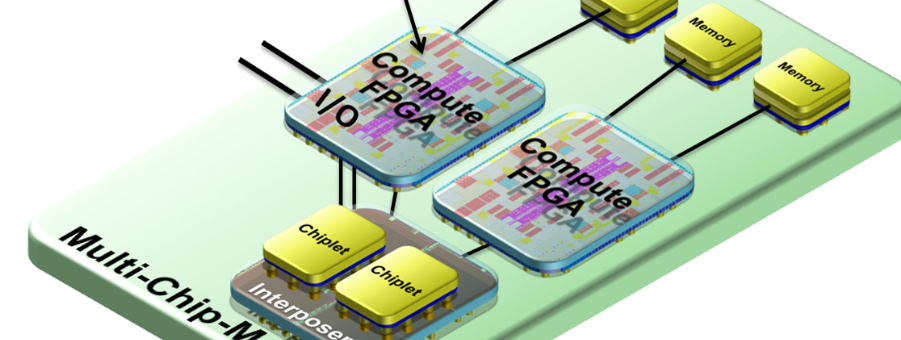

Hardware Support for Big Data

Big data workloads requires hardware acceleration through heterogeneous computing systems. The group will focus in developing new hardware architectures specialized for big data workloads.

-

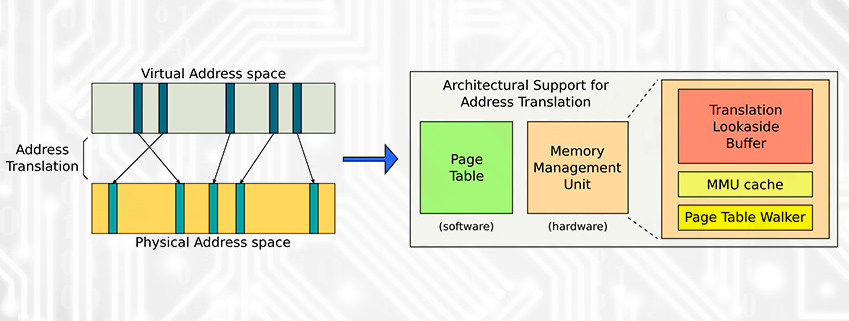

Improving Virtual Memory

Virtual memory provides many important benefits by introducing an indirection level between the virtual address space that the process sees and the physical memory that the operating system manages. However, virtual memory introduces high overheads that we seek to reduce in this project.

-

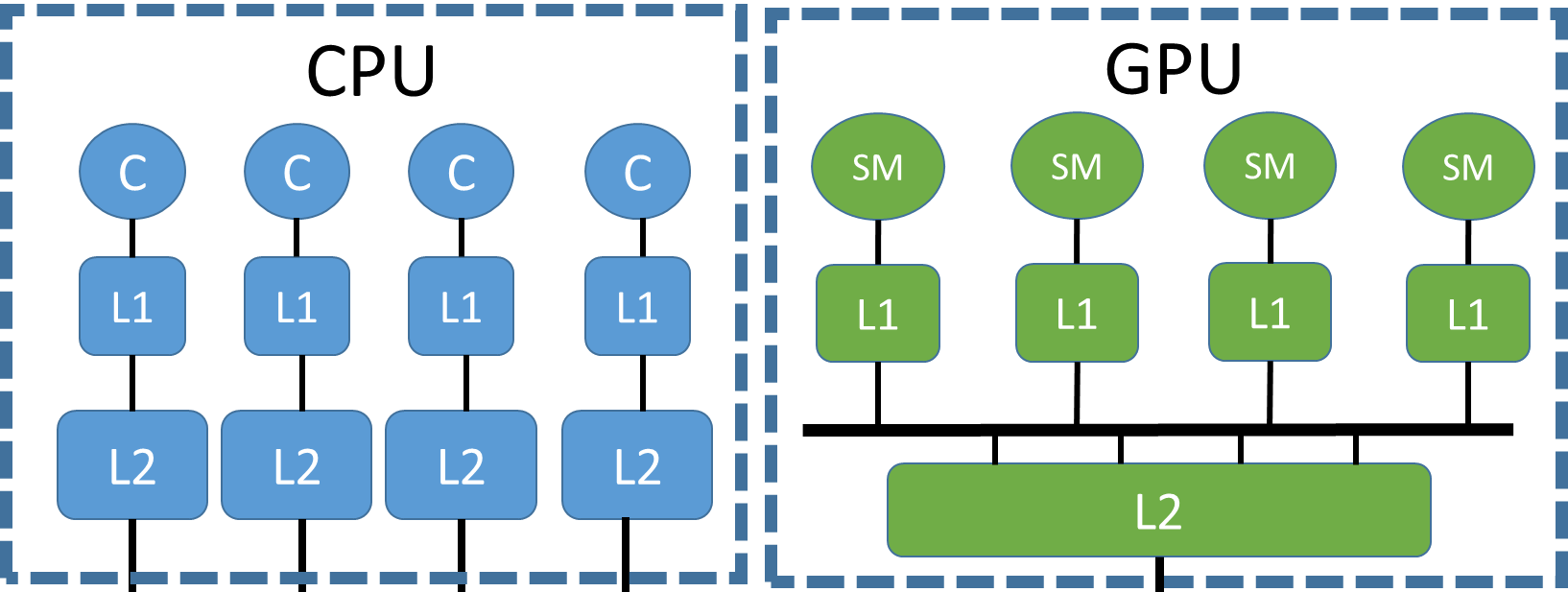

Memory hierarchy for GPU acceleration

Heterogeneous architectures have become the norm in the field of High Performance Computing. Many of such systems combine Graphics Processing Units (GPUs) and traditional multi-core processors to achieve many Teraflops of computational power.

-

Memory systems for HPC and AI

Next-generation memory systems for HPC and AI face significant challenges. These systems must deliver increased capacity and performance within a constrained power budget. We design and evaluate memory architectures that meet the requirements of these critical applications.

-

Microserver architectures and system software

With the end of Moore's Law, hardware architectures are becoming increasingly complex. We research low-level software mechanisms at the boundary between system architecture and system software to mitigate this complexity.

-

Mobile and embedded-based HPC

HPC systems are historically “recycling” ideas and technologies from larger markets: this has been true when HPC adopted x86 CPUs after the boom of desktop PCs in the 90’s, once again recently with GPUs boosted by the gaming market, etc.

-

Preemptive multiprogramming on GPUs

Architectural support for better GPU integration with the operating system - we are developing a simulation infrastructure to enable us to move toward implement "preemptible faults" in Streaming Multiprocessors.

-

Resilient architecture and runtimes

Reliability is becoming a first-class system design criteria in addition to performance and power. Hardware solutions by themselves will not be sufficient to mitigate the future error rates. The group investigates how to "marry" innovative hardware and software ideas for resilience.

-

Runtime aware architectures

Riding on Moore's Law (RoMoL) is a 5-year project funded by an ERC Advanced Grant awarded to Prof. Mateo Valero. RoMoL involves research in microarchitecture, runtime systems, compilers and programming languages.

-

SOftware research and development vehicles for New ARchitectures (SONAR)

The research activity of the SONAR group lays between the computer architecture (e.g. memory address translation, vector architectures) and high-performance computing (e.g. sparse linear algebra, parallel deep learning) areas.